Fixed-Point Designer 提供了丰富的数据类型和工具,用于在嵌入式硬件上优化和实现定点和浮点算法。它包括定点和浮点数据类型以及特定于目标的数值设置。使用 Fixed-Point Designer,您可以执行特定于目标的定点位真仿真。然后,您可以事先测试和调试溢出及精度损失等量化效应,之后再在硬件上实现设计。

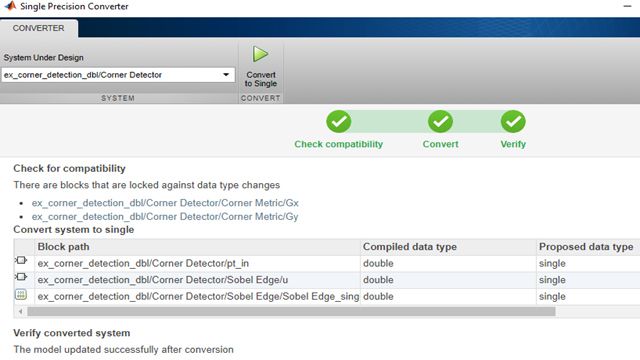

Fixed-Point Designer 提供的应用程序和工具可用于分析双精度算法,并将其转换为降精度浮点或定点。使用优化工具,您可以选择满足数值精度要求和目标硬件约束的数据类型。为了高效实现,您可以将运算量庞大的设计构造替换为硬件最优的模式,如压缩的查找表。

您可以直接从定点和浮点优化模型生成产品级 C 和 HDL 代码。

开始:

定点规格

为设计指定各种定点属性,包括特定于应用的字长、二进制小数点定标、任意斜率与偏差定标,以及舍入和溢出模式等控制细节。

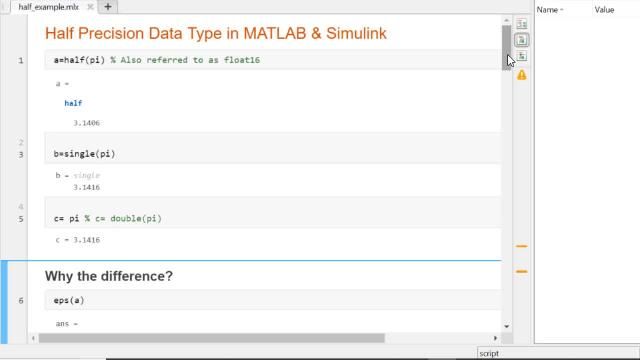

浮点仿真

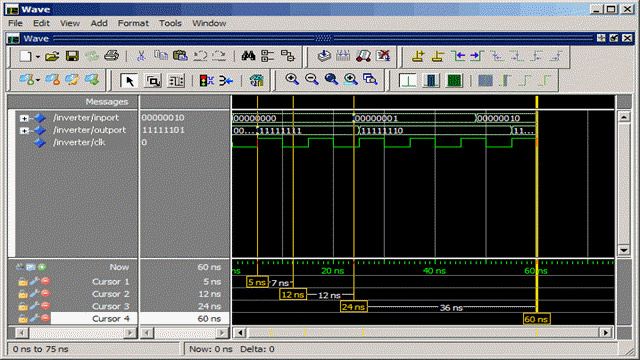

在仿真和代码生成中,为非规范浮点数(如下溢为零)进行目标硬件行为仿真。使用 MATLAB 和 Simulink 中的 fp16 半精度数据类型对有限精度浮点进行仿真。

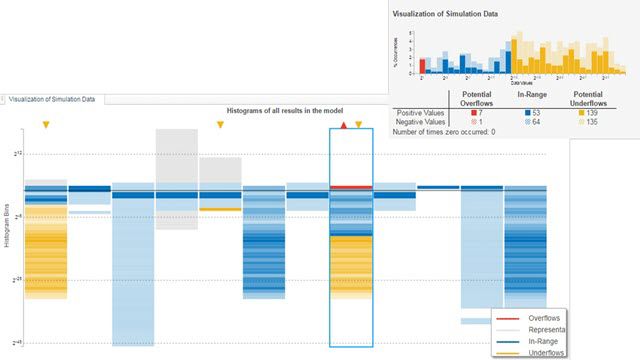

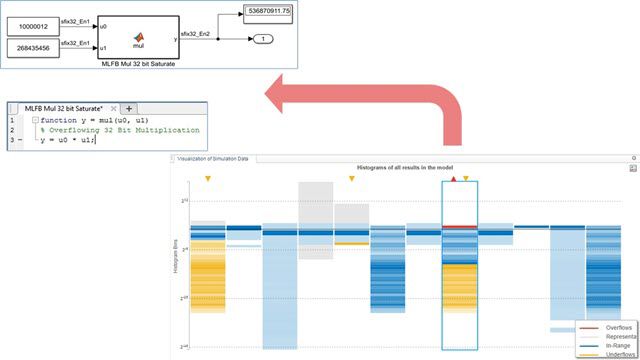

仪表化和可视化

借助整个模型范围内的自动仪表化收集仿真数据和统计量。收集范围数据来探索和分析您的设计。借助可视化来优化您的设计,以高效利用硬件资源。

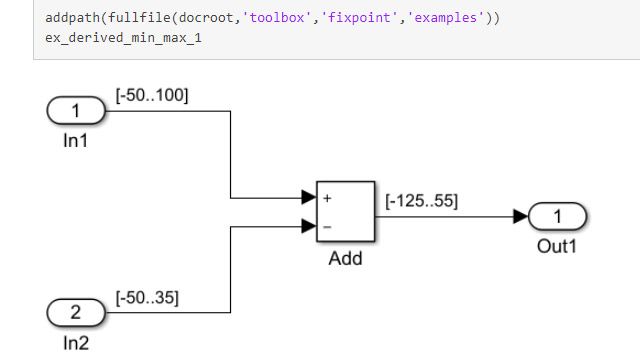

推导范围分析

根据对设计的数学分析推导出信号范围,并确定最坏情况下的范围或边缘情形,而无需创建全面涵盖所有情形的仿真测试平台。使用推导范围可以确保您的设计能够预防或处理所有可能的溢出。

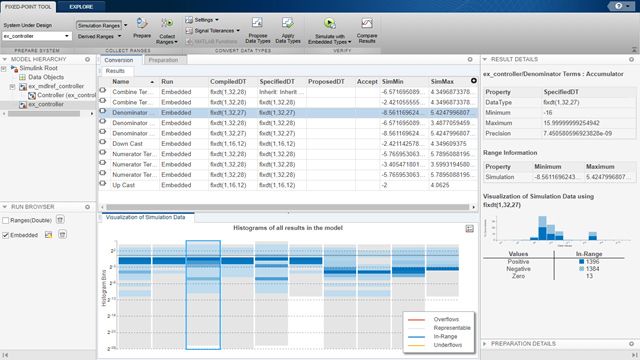

定点量化

在软件的引导下探索不同的定点数据类型及其对系统数值行为所产生的量化影响。观察设计中变量的动态范围,并确保转换后的算法在浮点表示和定点表示下具有一致的行为。

数据类型优化

自动遍历各种定点配置以选择最佳的异质数据类型,同时满足对系统数值行为的容差限制。该优化旨在使用定点数据类型将总位宽度降至最低,以实现高效设计。

函数逼近和查找表压缩

借助最优查找表,以数学方法逼近复杂的函数(如 sqrt 和 exp)或复杂的子系统。通过优化数据点和数据类型,压缩现有查找表来减少内存使用量。

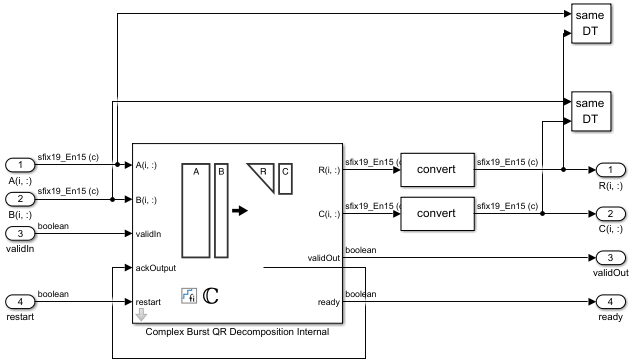

HDL 优化矩阵模块

定点 HDL 库包含一系列 Simulink 模块,可对线性方程组及核心矩阵运算(如 QR 分解)的设计模式进行建模,以在 FPGA 上获得高效硬件实现。使用 HDL Coder 为包含此类模块的设计生成 HDL 代码。

溢出和精度损失检测

快速识别、跟踪并调试溢出、精度损失以及范围或精度浪费的问题来源,并将您的设计与理想的浮点行为进行对比。保持模型和代码的比特精度一致可以最大限度地发挥基于模型设计的众多优势,帮助您在工作流早期发现上述问题。

测试数值边缘情形

生成涵盖多种数值情形的定点和浮点值,例如接近边界的值和非规范数,以测试算法的边缘情形,实现数值一致。生成具有不同维度和复/实性、使用整数、浮点和定点数据类型的信号的组合。