# MathWorks Vision for Systematic Verification and Validation

Bill Aldrich Senior Development Manager Simulink Verification and Validation, Simulink Design Verifier

© 2016 The MathWorks, Inc.

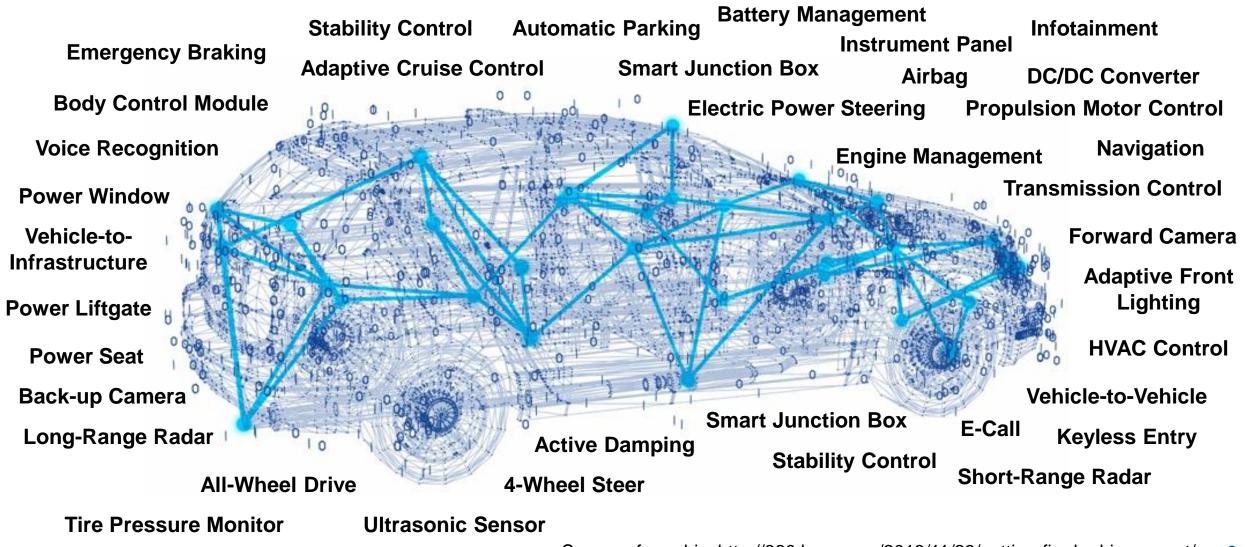

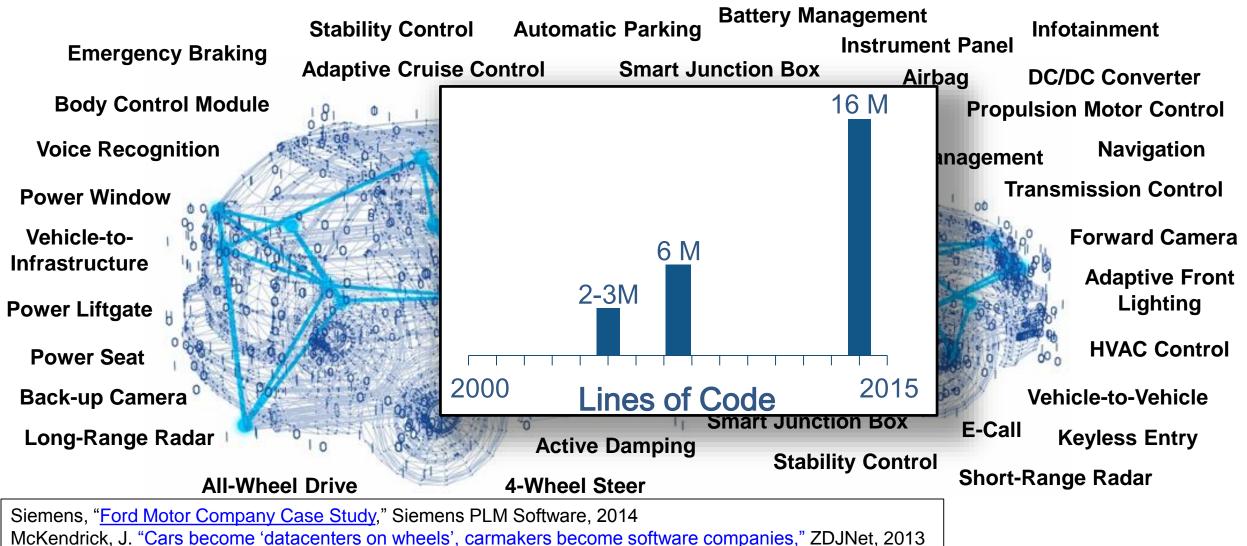

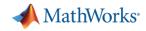

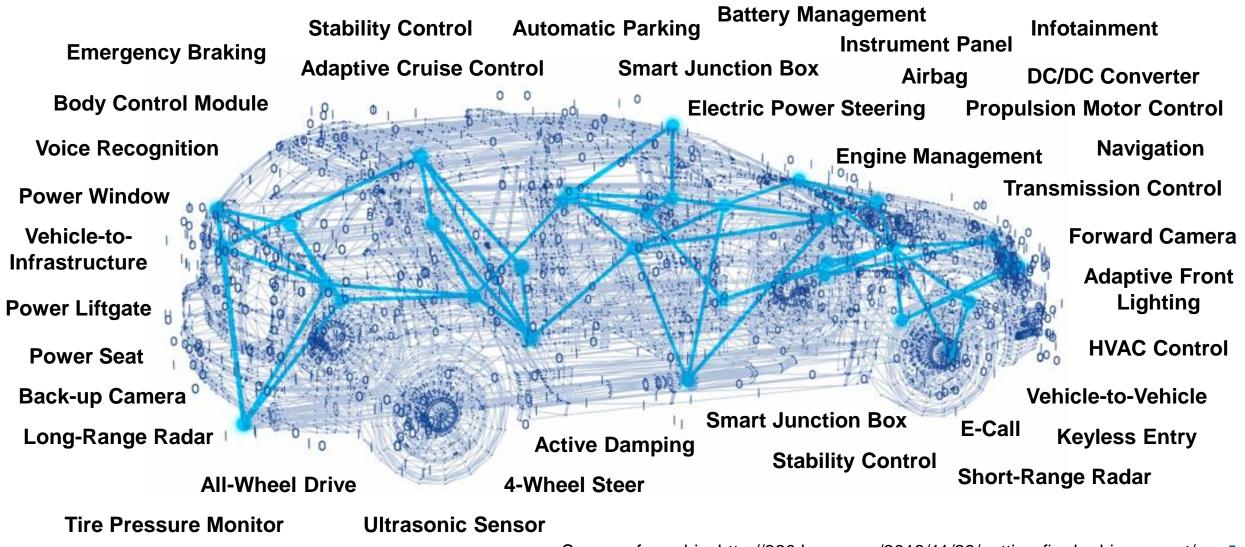

Source of graphic: http://360.here.com/2013/11/28/putting-firmly-drivers-seat/ 2

Source of graphic: http://360.here.com/2013/11/28/putting-firmly-drivers-seat/ 5

### **Development Challenges**

- Representing complex systems

- Coordinating work across teams

- Working efficiently

- Ensuring quality

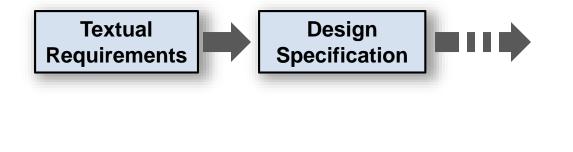

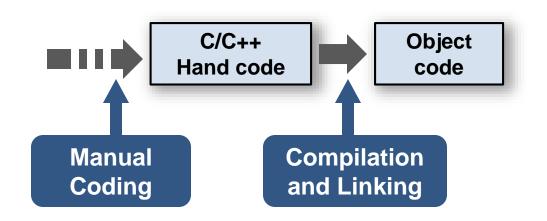

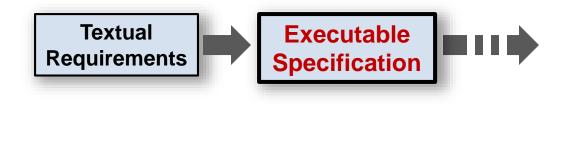

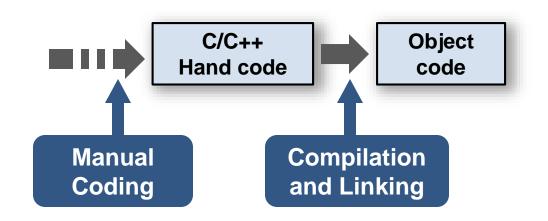

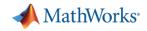

### **Traditional Development Process**

### **Models for Specification**

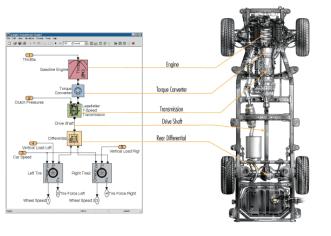

### Model Abstraction – Work at an appropriate level of detail

#### Simscape Multibody

### Simscape Driveline

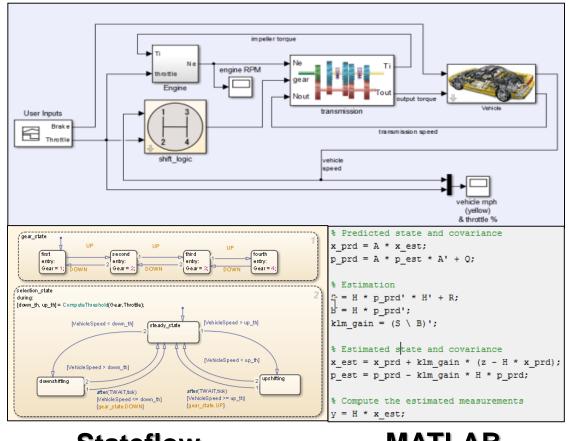

#### **Stateflow**

#### MATLAB

#### Simulink

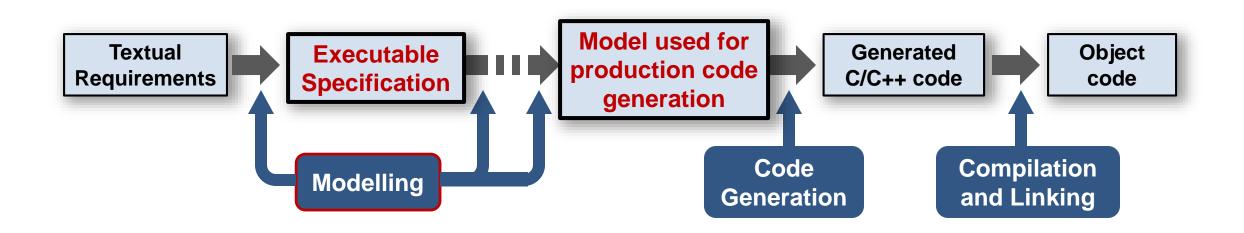

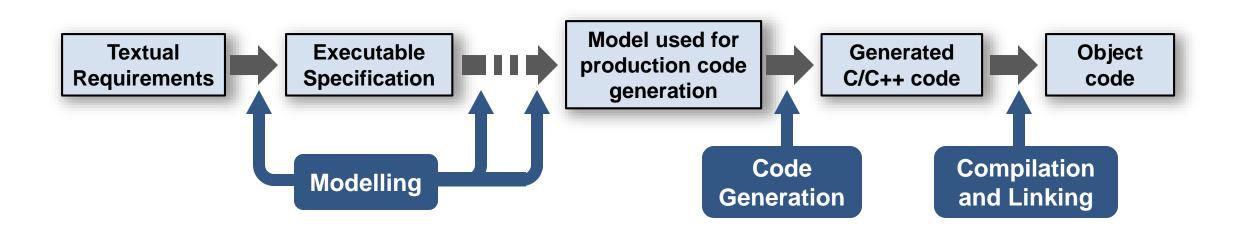

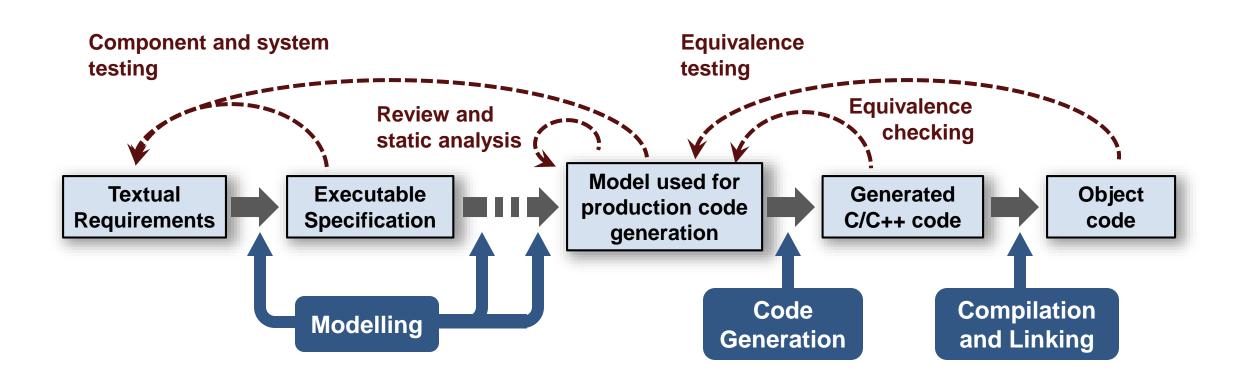

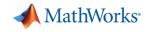

### **Complete Model Based Design Workflow, Concept to Code**

### **Complete Model Based Design Workflow, Concept to Code**

## How do you ensure correctness?

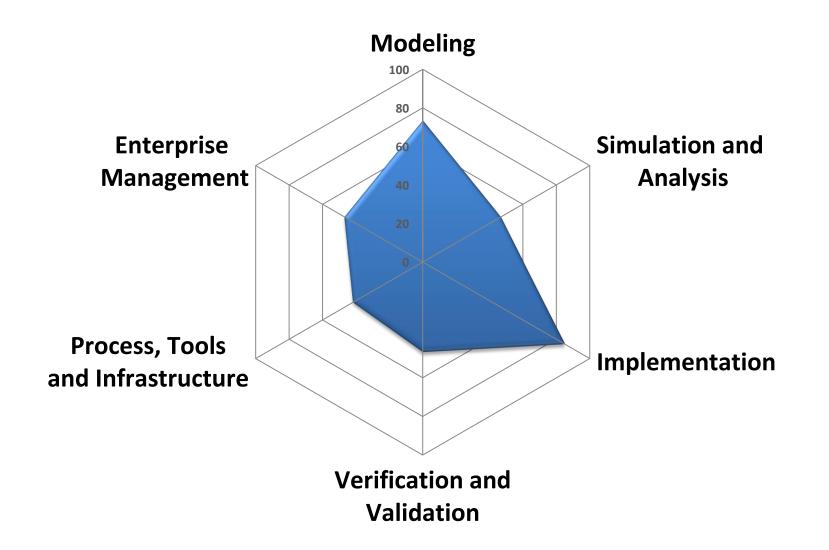

### **Model-Based Design Maturity, Automotive Industry**

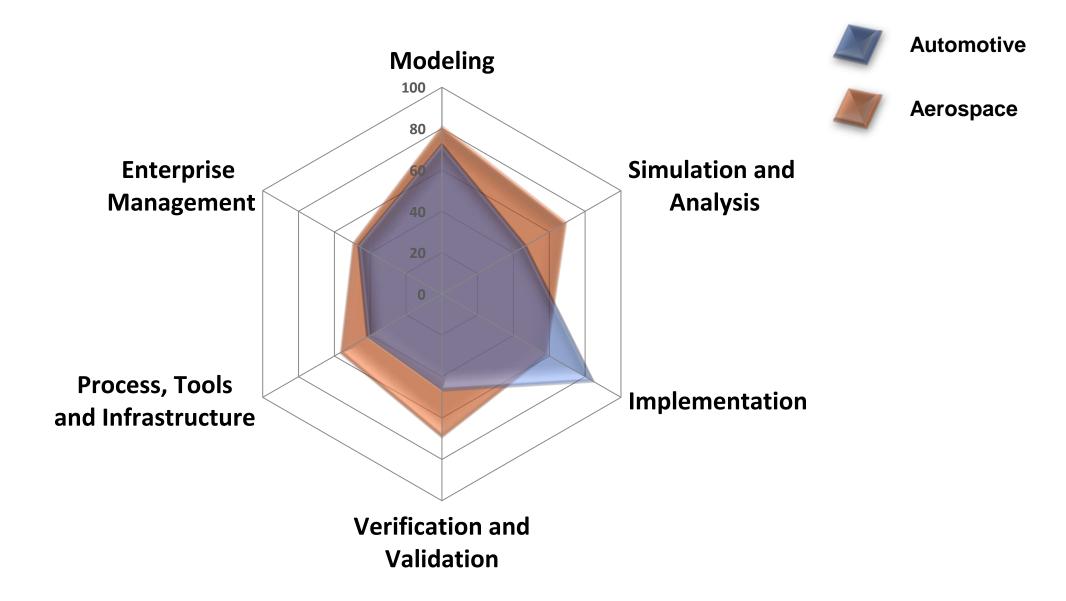

### **Model-Based Design Maturity, Automotive and Aerospace**

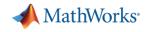

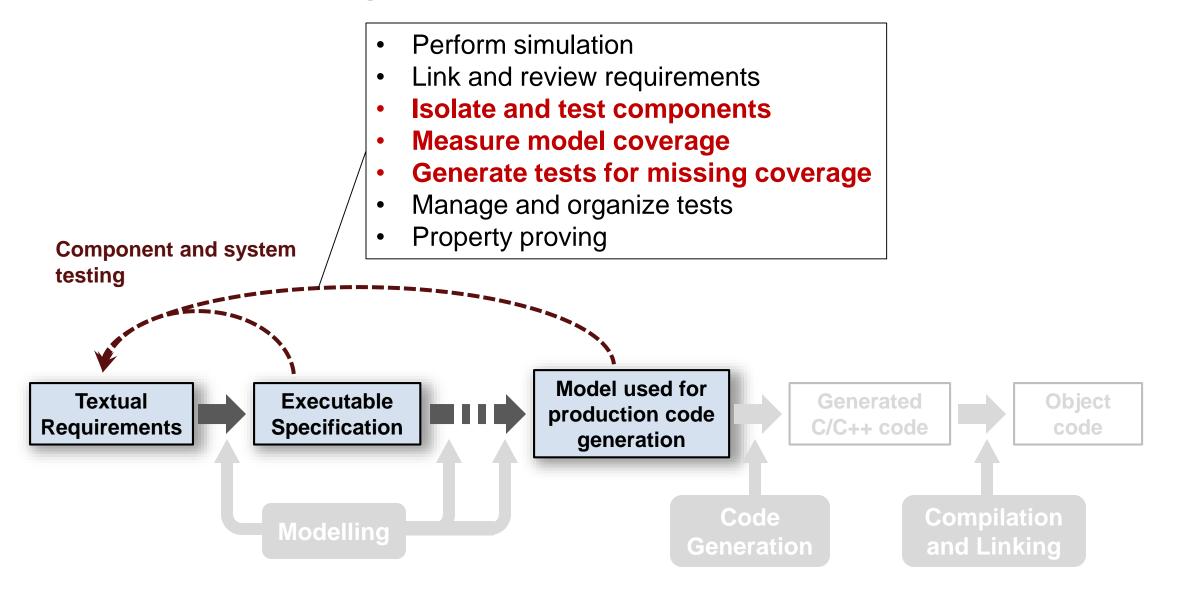

### **Ad-Hoc Simulation: Explore Behavior Virtually**

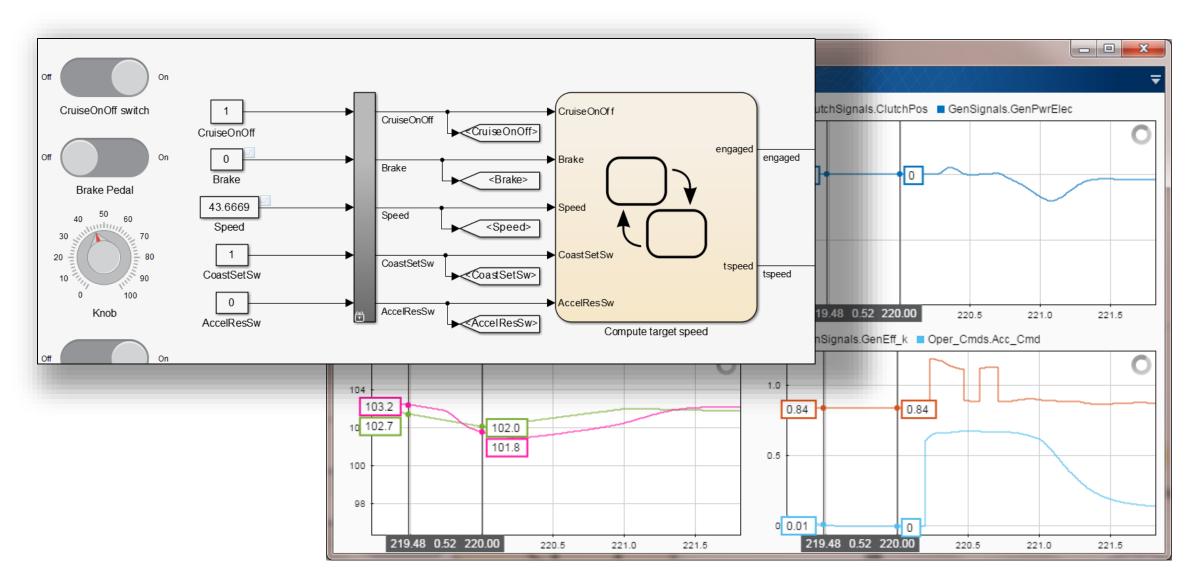

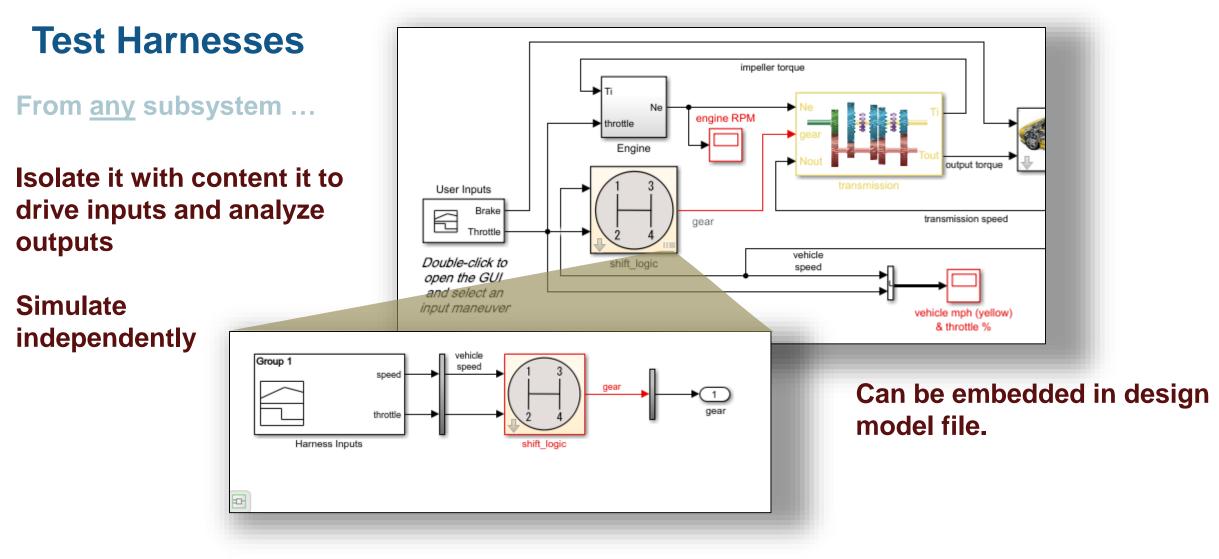

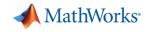

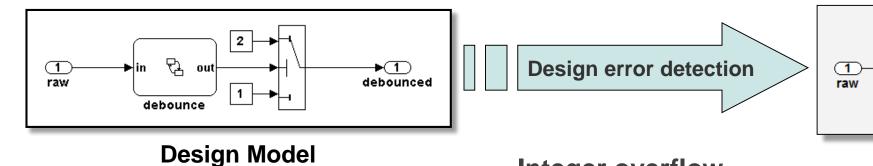

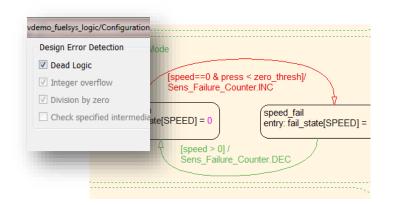

### **Test Harnesses**

From <u>any</u> subsystem ...

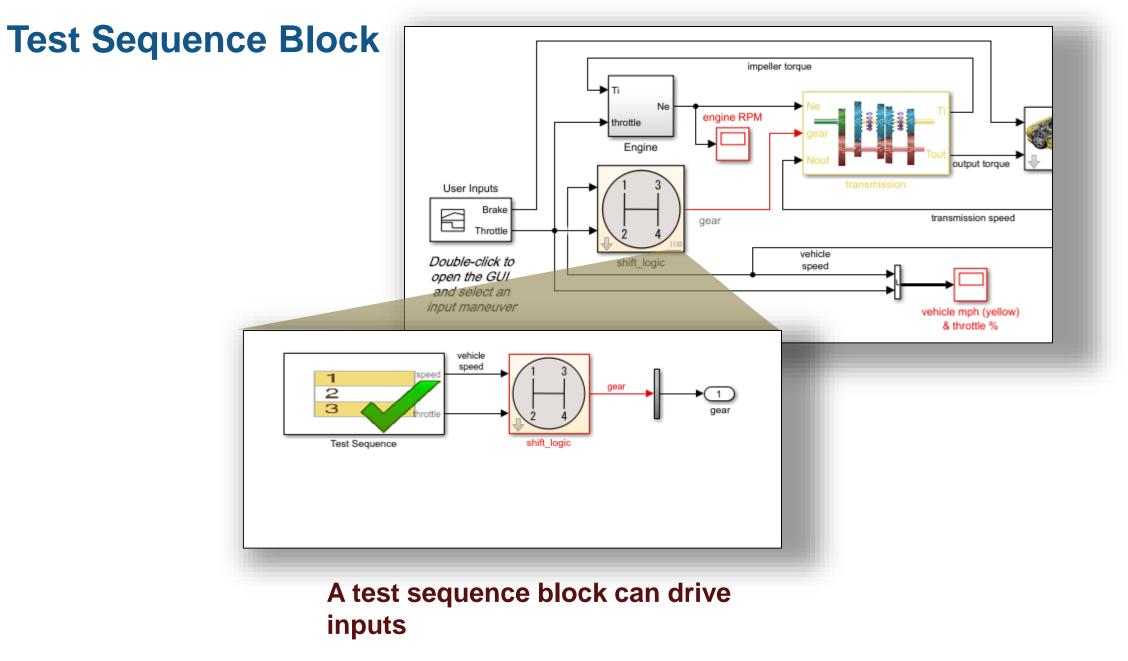

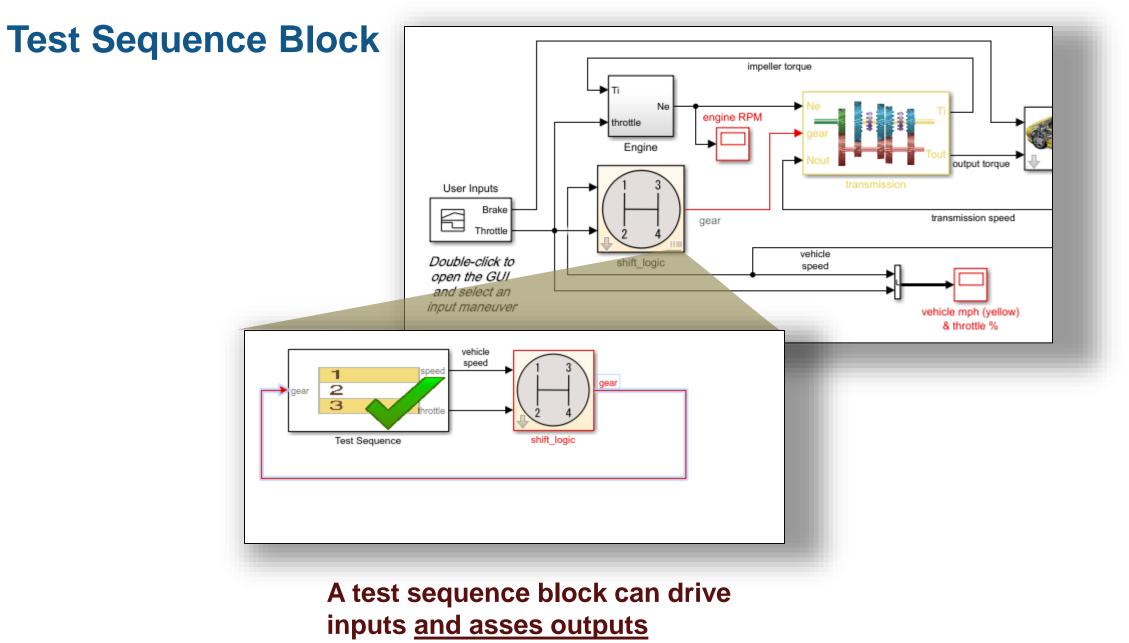

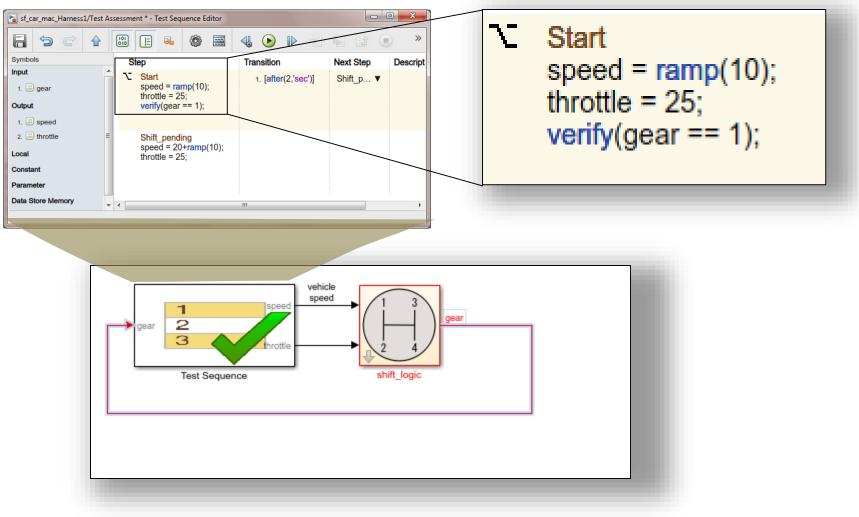

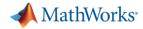

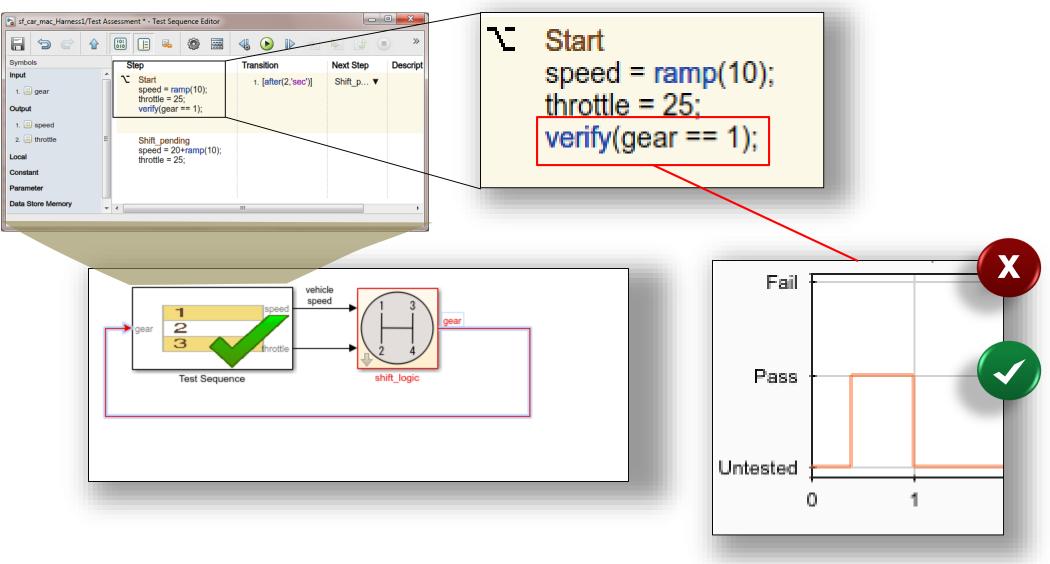

### Test Sequence Block Syntax

### **Defining Pass/Fail Criteria**

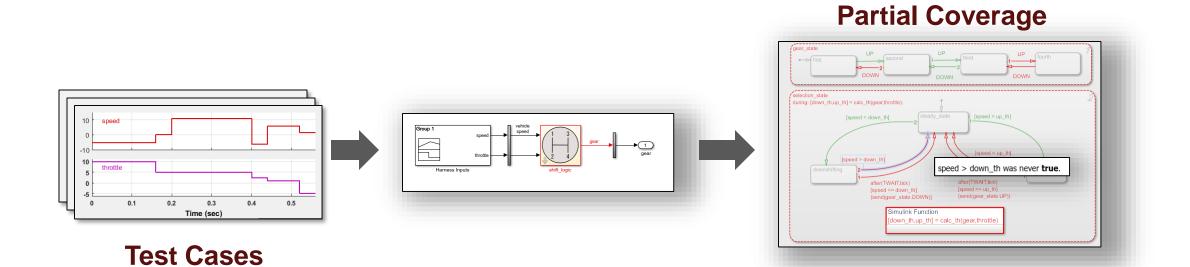

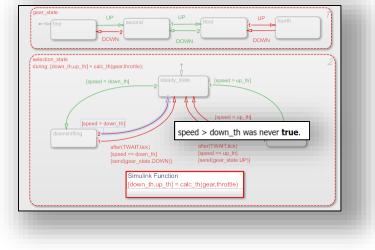

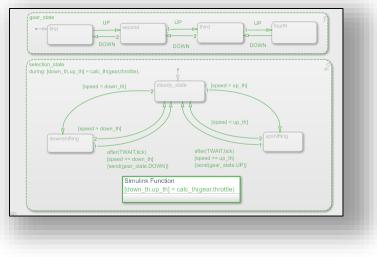

### **Model Coverage**

#### **Identify testing gaps:**

- Untested switch positions

- Subsystems not executed

- Transitions not taken

- Many more ...

| gear_state                                            | UP second UP third UP fourth DOWN DOWN                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| selection_state<br>during: [down_th,up<br>down_shifti | p_th] = calc_th(gear,throttle);<br>[speed < down_th]<br>[speed > down_th]<br>[speed > down_th]<br>[speed > down_th]<br>[speed > down_th]<br>[speed < up_th]<br>[speed < up_th]<br>[speed > down_th was never true.<br>after(TWAIT,tick)<br>[speed <= down_th]<br>[speed >= up_th]<br>[send(gear_state.DOWN)]<br>[send(gear_state.DOWN)] |

|                                                       | Simulink Function<br>[down_th,up_th] = calc_th(gear,throttle)                                                                                                                                                                                                                                                                           |

26

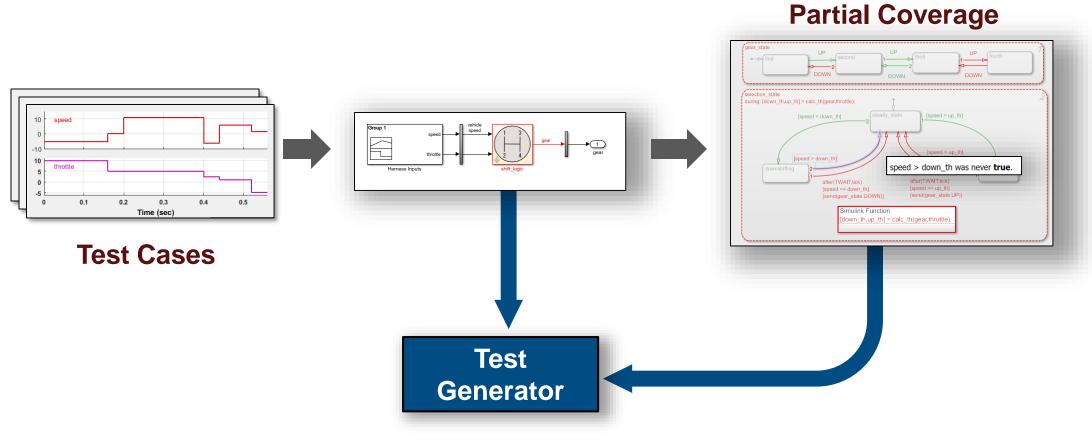

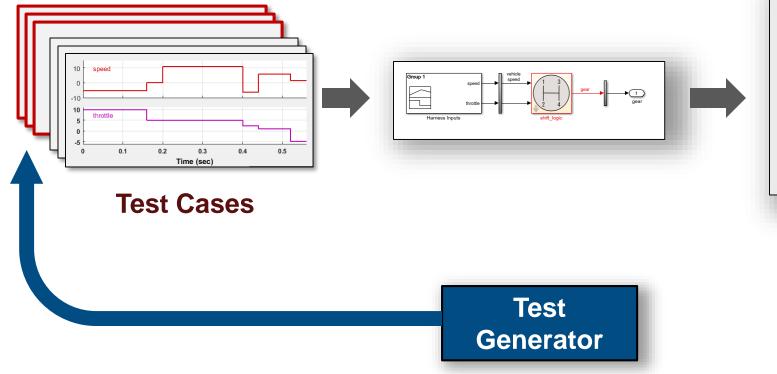

**Simulink Design Verifier**

#### **New Test Cases**

#### **Partial Coverage**

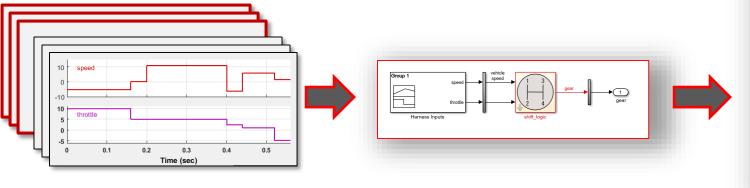

**Simulink Design Verifier**

#### **New Test Cases**

#### Full Coverage

**Test Cases**

●1)

debounced

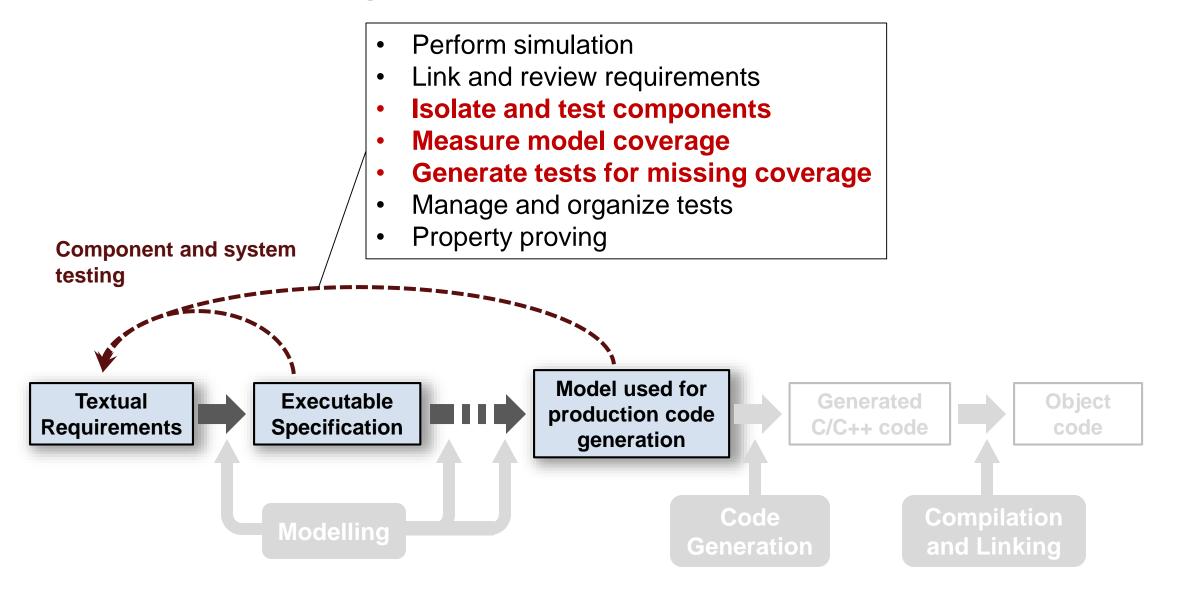

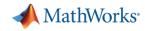

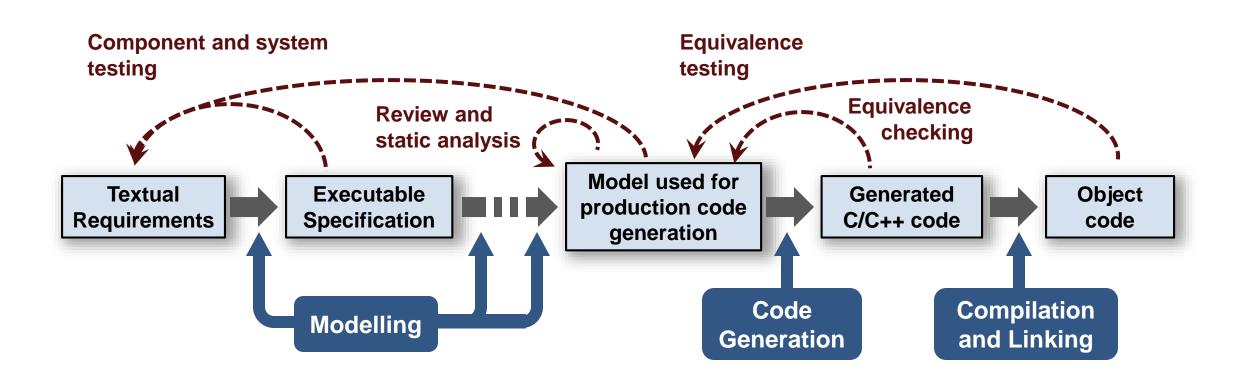

### **Detecting Hidden Run-Time Design Errors**

- Integer overflow

- Division by zero

- Array out-of-bounds

- Range violations

- Dead Logic

#### **Highlighted Model**

2

1

₽3

debounce

out

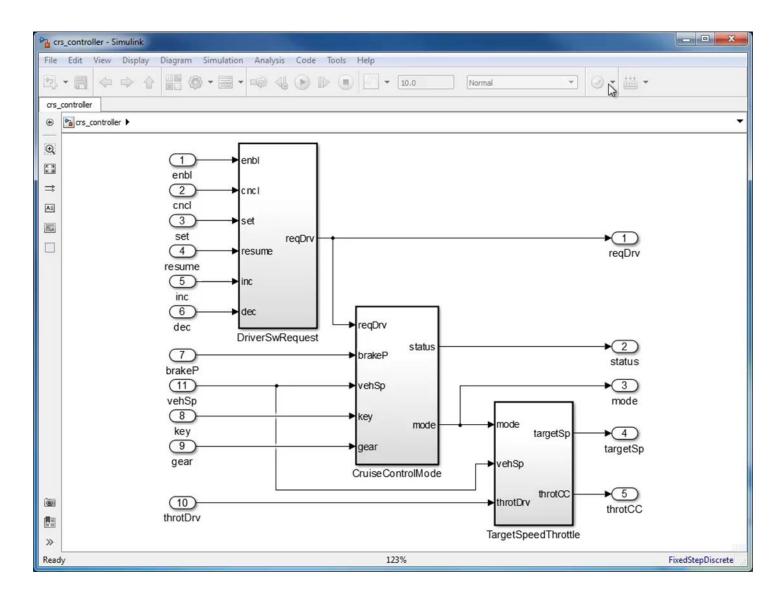

### **Detecting Hidden Run-Time Design Errors**

### **Detecting Hidden Run-Time Design Errors**

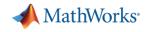

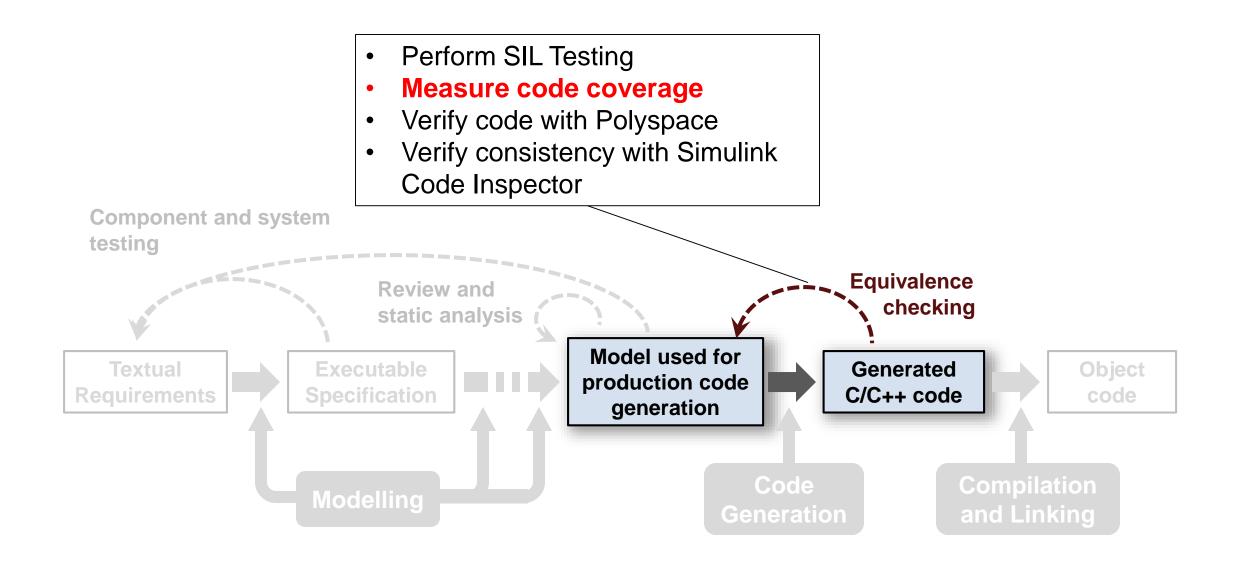

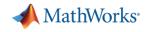

### **Coverage for Generated Code (R2016a)**

**Generated Code Coverage**

### **Coverage for Generated Code (R2016a)**

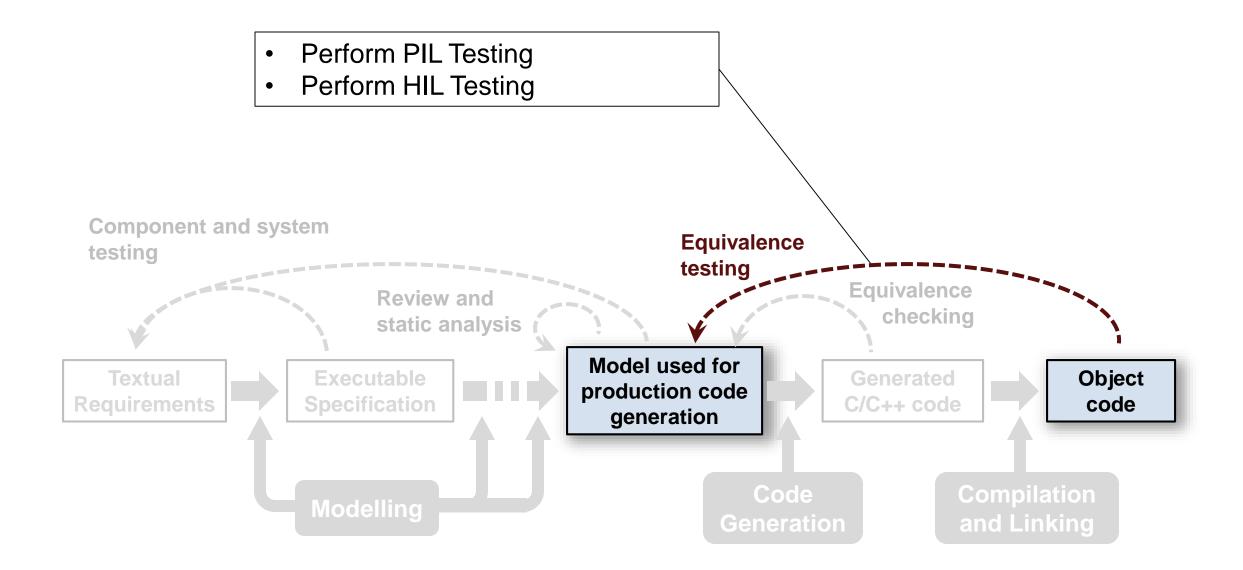

### **Systematic Verification**

- Ensure that verification is systematically performed across:

- All requirements

- Complete model structure

- Complete code structure

- All design behaviors

**Simulink Design Verifier**

Simulink Test

Simulink Verification & Validation

### **Test and Verification**

- Essential

- Expensive Pain Points

- Complex

### **Test and Verification**

• Essential  $\rightarrow$  More Complete • Expensive  $\rightarrow$  Faster • Complex  $\rightarrow$  Simpler

### **Thank You!**